看到文章的标题“射频电路中的电源设计要点”,相信有部分读者已经想到了,本文即将讲述的是一个综合的问题:结合和射频电路设计与电源电路设计。在我接触的同事,朋友当中,很多射频工程师都是埋头苦干,专心研究射频技术领域,却往往忽略了其他部分可能会造成的影响,电源电路就是其中的很重要的部分。所以我坚持认为,射频工程师要考虑到系统级别,包括时钟,电源,甚至数字电路部分,这样才能实现最优化设计,最佳性能与最高效率。我抛出这样的观点也许会遭到很多人的反对,不过不要紧,遇到问题时再来看这篇文章吧。

我准备重点讲述两部分的内容,第一部分是低噪声放大器的电源电路设计要点,第二部分是射频功率放大器的电源电路设计要点。由于近几年的产品设计采用的都是SoC方案,所以很少有机会接触独立的VCO,PLL,混频器,调制/解调器等,以后有机会接触再做总结。关于射频SoC的电源电路设计,过段时间我会单独撰写。

我准备重点讲述两部分的内容,第一部分是低噪声放大器的电源电路设计要点,第二部分是射频功率放大器的电源电路设计要点。由于近几年的产品设计采用的都是SoC方案,所以很少有机会接触独立的VCO,PLL,混频器,调制/解调器等,以后有机会接触再做总结。关于射频SoC的电源电路设计,过段时间我会单独撰写。

低噪声放大器电源电路设计

低噪声放大器位于接收机的最前端,对于整体的接收灵敏度的影响是最大的。从灵敏度表达式

![]() 可以看出,对于给定的通信协议,提高灵敏度的方法是尽可能降低放大器的噪声系数NF,当然我们还需要尽可能高的增益,这是很矛盾的。为了降低低噪声放大器的噪声系数,我们首先要选用合适的管子,然后选择合适的直流工作点,进行合理的射频电路设计,进行反复的测试,调试……

可以看出,对于给定的通信协议,提高灵敏度的方法是尽可能降低放大器的噪声系数NF,当然我们还需要尽可能高的增益,这是很矛盾的。为了降低低噪声放大器的噪声系数,我们首先要选用合适的管子,然后选择合适的直流工作点,进行合理的射频电路设计,进行反复的测试,调试……

但是你是否想过,低噪声放大器的电源设计?

1. 排除不确定因素,使用LDO为LNA供电

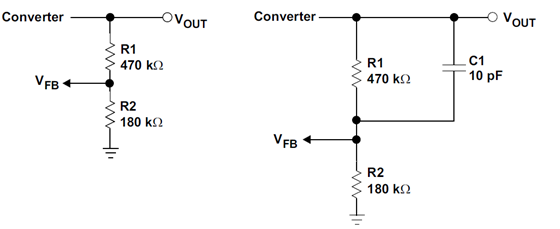

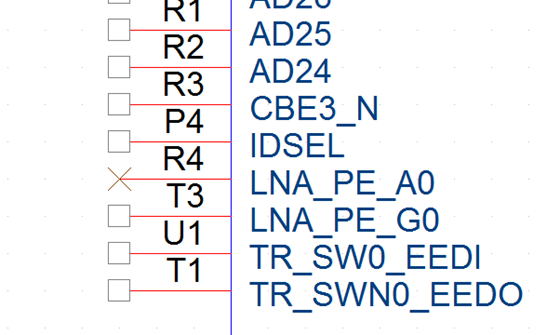

在现有的基于SoC的设计方案中,LNA的供电都是由SoC上相应的控制管脚实现的,如下图中的LNA_PE_G0就是用于控制LNA供电的。

那么,如果LNA_PE_G0携带着很多噪声,射频电路设计的再好也没用了,而且可悲的是,我们没有任何手段保证LNA_PE_G0这种来自SoC的信号的纯净度。

所以,我认为,LNA的供电最好使用具有较高PSRR(电源抑制比)的LDO(线性稳压器)来实现。例如,TI的TPS718xx,TPS719xx就是一种高性能的LDO,电源抑制比可达65dB@1kHz, 45dB@1MHz,比较适合在低噪声放大器中使用。

2. 电源走线依据“先过电容”的原则

不会Layout的工程师不是好工程师,射频电路性能的好坏与Layout关系很大。在PCB Layout过程中,要时刻建立一种电流流向的概念,即电流从哪里来,要到哪里去,怎样让电流回路最小……

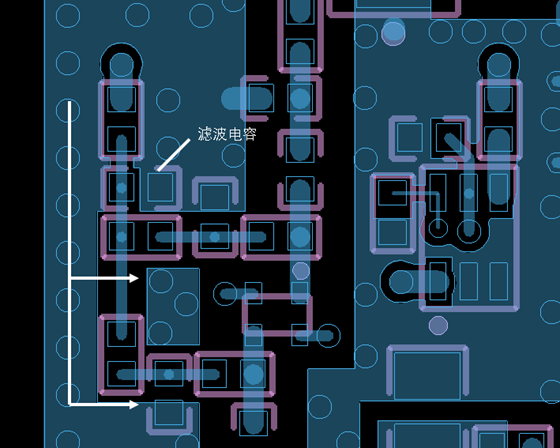

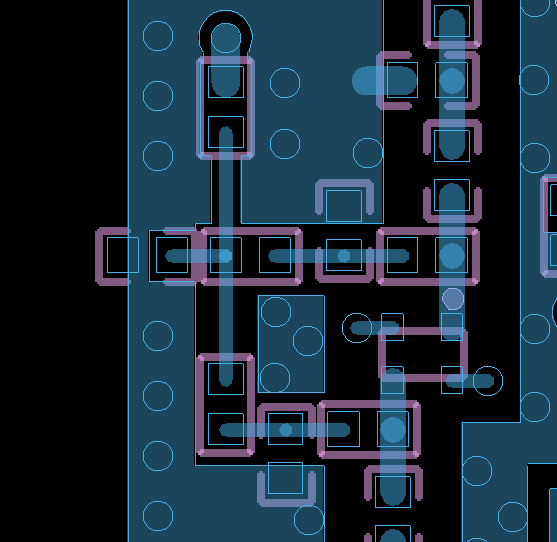

对于低噪声放大器,滤波电容是少不了的,我们一定要保证电流先流过滤波电容,再进入放大器。看看下面的两张图片,自己体会一下。

如果听取了我的建议,在设计中选用了LDO为低噪声放大器供电,那么你就千万别想着通过控制LDO的使能脚来实现低噪声放大器的打开/关闭了,反应再快的LDO也赶不上Switch,就像再牛的香水也干不过韭菜合子一样。因此,这个时候,最好使用模拟开关来为LNA供电,可供选择的型号有很多,我在这里不多作介绍。

如果不使用模拟开关,那么你遇到的一个大问题便是数据吞吐量的大幅下降。

射频功率放大器的电源电路设计

相对于低噪声放大器,射频功率放大器的电源设计有更多的问题需要注意,在本文中我只讨论两点,一是功率余量,二是电源的瞬态响应。其实关于PA的电源电路设计我有一项专利,在这里不方便透露。

1. 射频功率放大器的电源功率余量

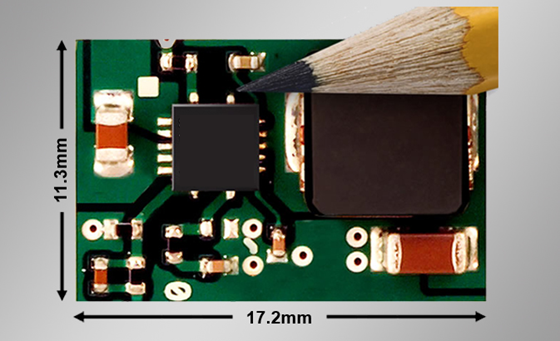

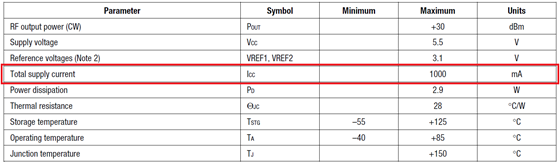

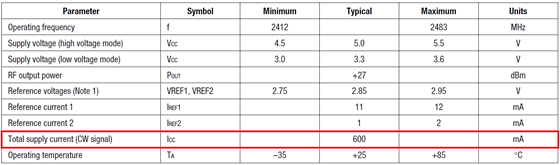

由于功率放大电路需要消耗较多的电源功率,考虑到系统功耗,我们只能采用DCDC为PA供电。当你阅读PA的Datasheet时,请务必读懂其关于功率消耗的说明。在一份PA的Datasheet中,通常会给出静态电流,典型输出功率下消耗的电流以及Absolute Maximum Current Consumption,如下图。

某PA最大消耗电流

? 我建议,所有关于射频功率放大器功耗的计算,取其功率消耗的最大值,并预留20%的余量。

? 我建议,所有关于射频功率放大器功耗的计算,取其功率消耗的最大值,并预留20%的余量。

2. DCDC的快速瞬态响应

可能有很多工程师不知道“瞬态响应”这样的指标,瞬态响应描述的是DCDC应对快速变化的负载的响应能力。对于CPU内核电压,或者射频功率放大电路,瞬态响应这项指标相当重要。

IEEE 802.11标准中,对于设备的输出功率从10%上升到90%的时间做了规定,为了不影响产品性能,我们当然希望上升时间越短越好。射频电路本身往往不会对上升时间造成限制,但是这就对电源电路提出了较高的要求:必须在极短的时间内响应并提供最够的输出功率。

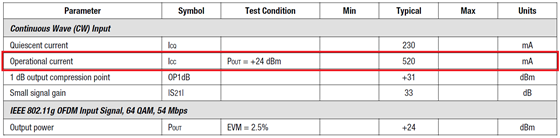

观察下图中两种DCDC反馈电路的拓补结构,不难发现,右侧比左侧的反馈电路多了一颗10pF的电容。这颗电容可不简单,我们将在后面看到这颗电容的用途,这颗电容称为“前馈电容”。

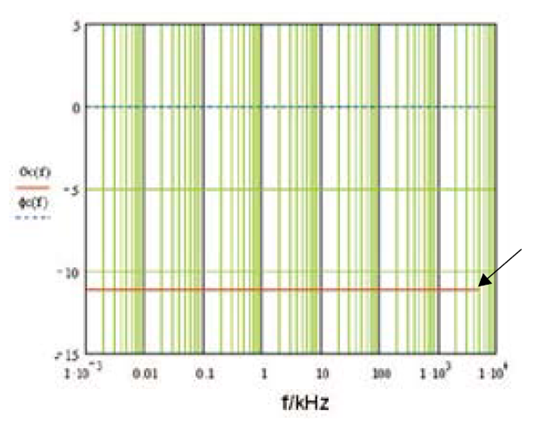

无前馈电容时,DCDC的反馈网络由两颗电阻组成,用于设定DCDC转换器的输出电压,其传递函数如下图所示。

无前馈电容时,DCDC的反馈网络由两颗电阻组成,用于设定DCDC转换器的输出电压,其传递函数如下图所示。

无前馈电容的传递函数

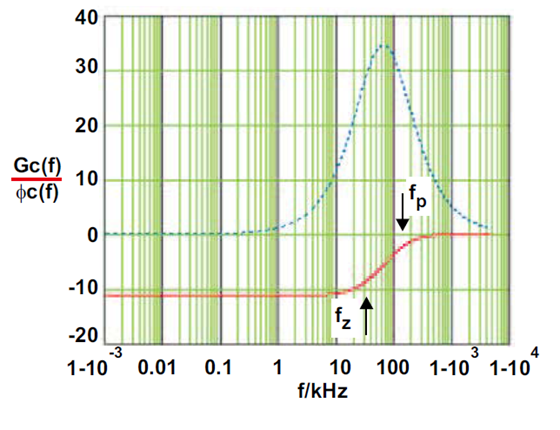

增加了前馈电容后,DCDC转换器可以更高效地响应高频扰动。

有前馈电容的传递函数

比较两种图形不难发现,两种反馈结构在低频段具有一致的响应曲线;在中高频区域,C1的通路阻抗降低使得输出的电源扰动降到最低,有效的提供了更高的增益和相位。对于运行中的DCDC电源转换器来说,增益及相位的增加促使转换器对瞬变负载产生更快的响应。

发表评论